Projects

We can optimize the performance of real-time applications with manycore vision processors, but they consume too much power. We propose a manycore design where the image processing of each core is enclosed with virtual FPGA architecture to facilitate high-performance optimization and power efficiency.

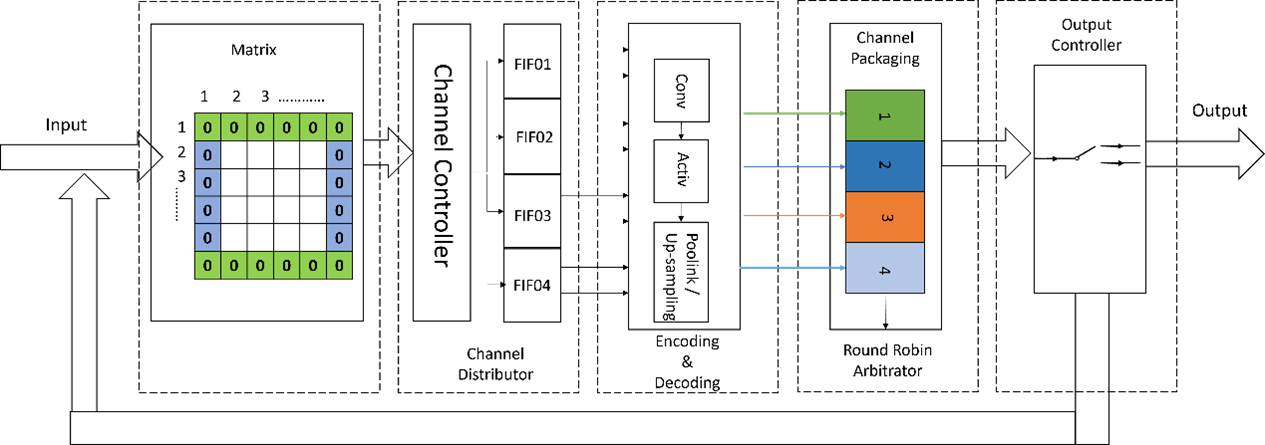

We look at the different autoencoders available and use the convolutional autoencoder in both FPGA and GPU-based implementations to process noisy static MNIST images. The encoded images are further analyzed with a convolutional autoencoder architecture comprising of matrix operation, channel distributor, encoding module, round-robin arbitration, and output controller blocks.

Proposed a partial reconfiguration flow for Radiant, Propel and Propel Builder software (Devices: ECP5, CertusPro-NX).

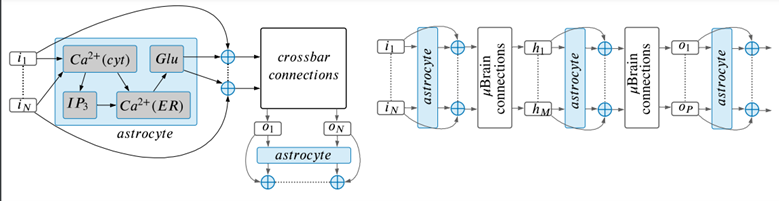

We propose a design methodology to facilitate fault tolerance of deep learning models. We implemented the astrocyte design, the baseline 𝜇Brain and crossbar designs on Xilinx VCU128 development board.

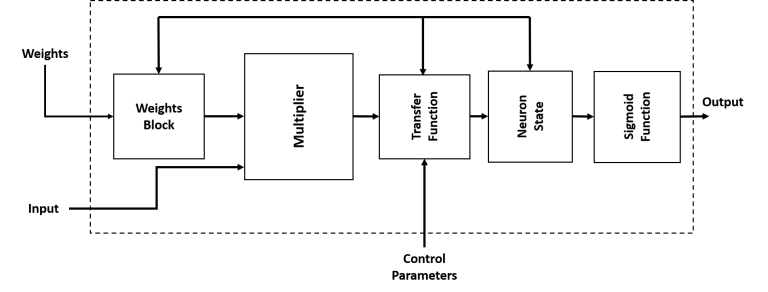

We propose an analog and digital coupled neuron model comprising of individual excitatory and inhibitory neural circuit blocks for a low-cost and energy-efficient system. To demonstrate excellent design principles, the hardware neural system was implemented on Xilinx Kria KV260 FPGA. The mentioned system produces a hardware platform comprising a high-performance XCK26-SFVC784-2LV FPGA chip. The number of hardware neurons specified in this study is realized in a single core of the KV260 development board.

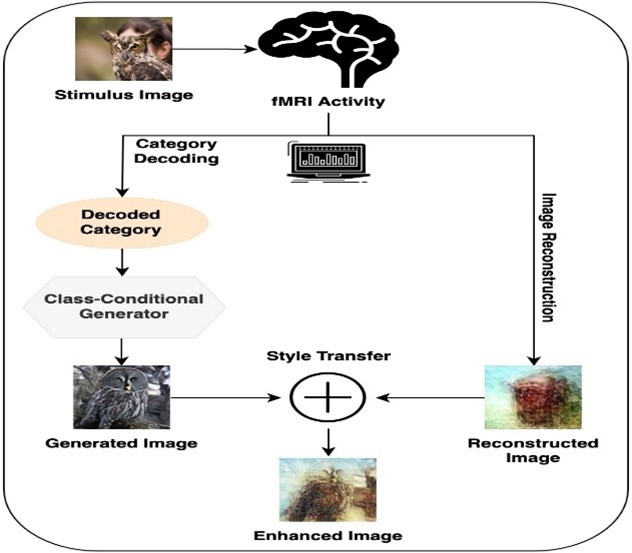

We present a novel approach for enhanced image reconstruction, in which existing methods for object decoding and image reconstruction are merged together. This is achieved by conditioning the reconstructed image to its decoded image category using a class-conditional generative adversarial network and neural style transfer.

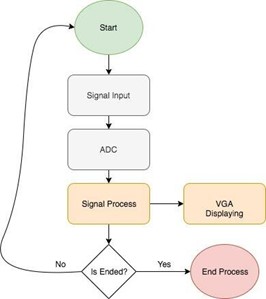

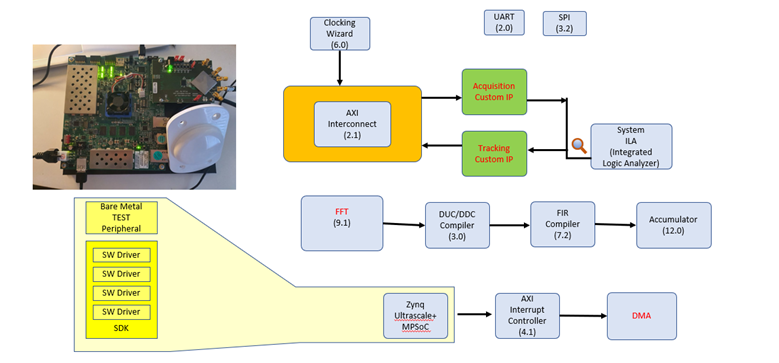

This project has the acquisition and tracking system design for the Global Navigation Satellite System (GNSS) receiver. GNSS receivers are primarily designed to process signals transmitted from satellites. These signals comprise carrier components, code phase component, and encrypted navigation data. The processing block must accurately track the phase of the incoming code component and the frequency of the incoming carrier signal in order to properly demodulate the navigation data. This receiver design is made up of a Radio Frequency (RF) Front-End and Field Programmable Gate Array (FPGA), with NT1065 from NTLab and Xilinx ZCU104 MPSoC as its core chips.

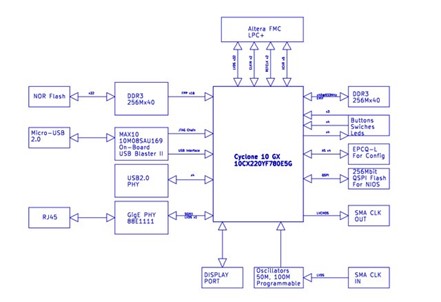

Our aim was to customize high-performance FMC expansion cards designed for Cyclone 10 GX FPGA-based video and network application development.

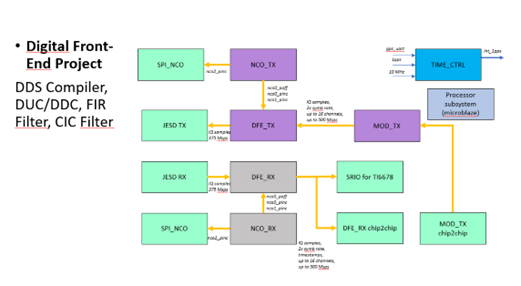

Digital Front-End Project Write Matlab code and IP core design include; DDS Compiler, DUC/DDC, FIR Filter, CIC Filter Completed

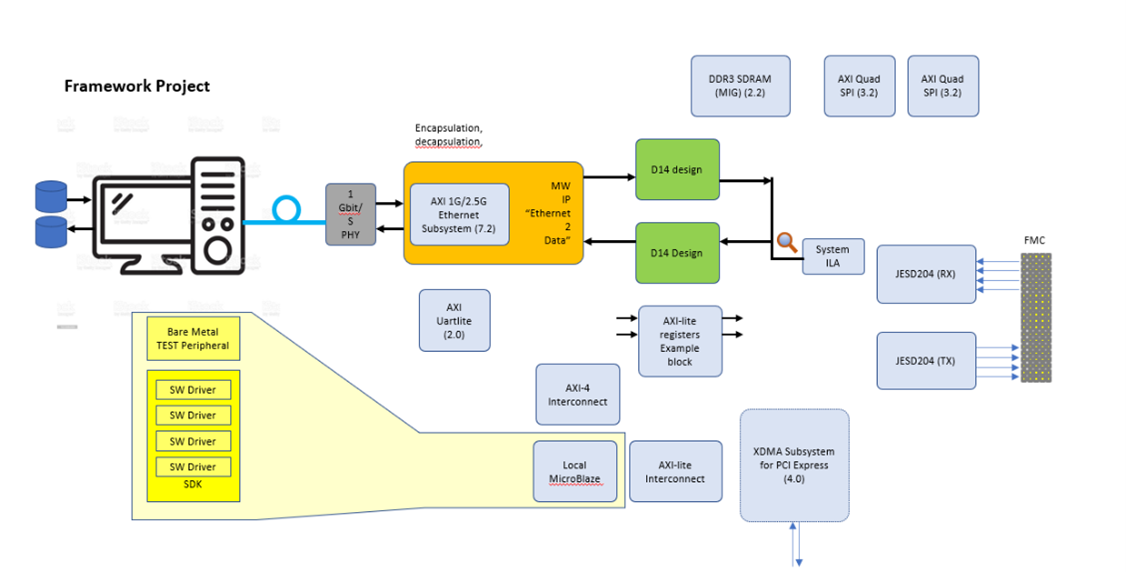

MicroBlaze Soft Processor Core- (ZCU104, KC105, VC709 ) IP core design include JAMMER project; Register FIFO, AXI-4 Lite, DDR4RAM, Quad SPI, JESD204B (Tx-Rx), Uart Lite, XDMA for PCI Express

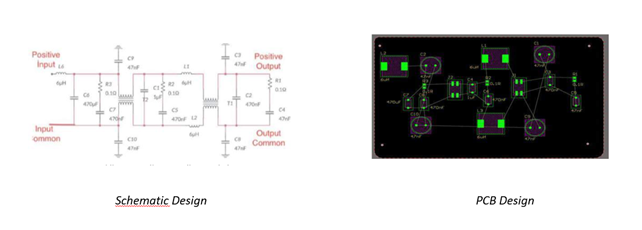

This EMI filter design with a minimum loss of 55 dB at 500kHz in MIL-STD-461F standards has been designed and simulated with two-port circuit approach and parametric sweep analysis methods. As a result, an EMI filter was obtained with the Faraday cage and shielding, taking into account the physical requirements and MIL-STD-461F standards.